Two-dimensional indium selenide wafers for integrated electronics

Biao Qin; Jianfeng Jiang; Lu Wang; et al. Two-dimensional indium selenide wafers for integrated electronics. Science (IF 56.9 SCI Q1 中科院 综合性期刊1区), 2025. DOI:10.1126/science.adu3803. main, sm.

InSe 薄膜生长难点:

- 相多样性:至少 InSe, In2Se3, In4Se3, In6Se7 四种稳定相。

- 结晶性差:难以保持 In 和 Se 的化学计量平衡,~500 ℃ 生长时 Se 蒸气压比 In 高七个量级。

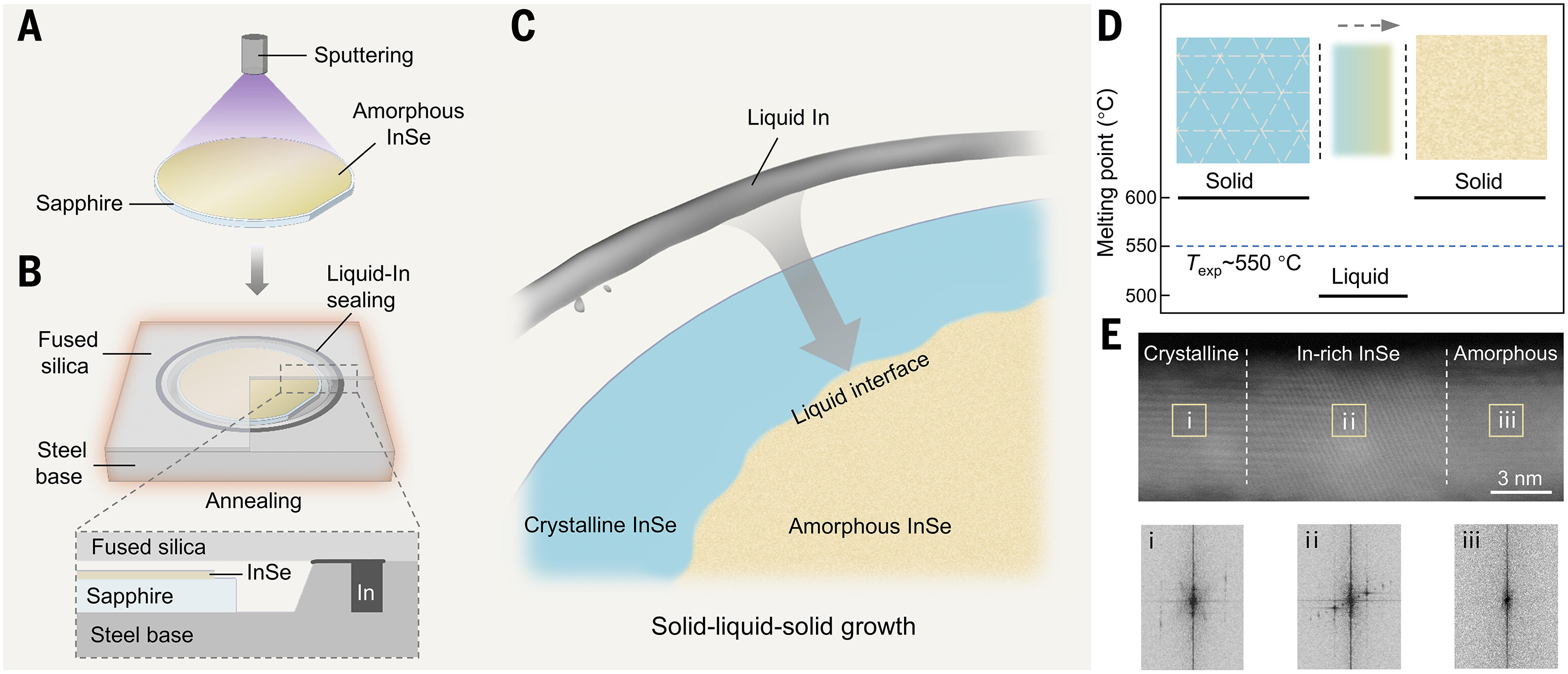

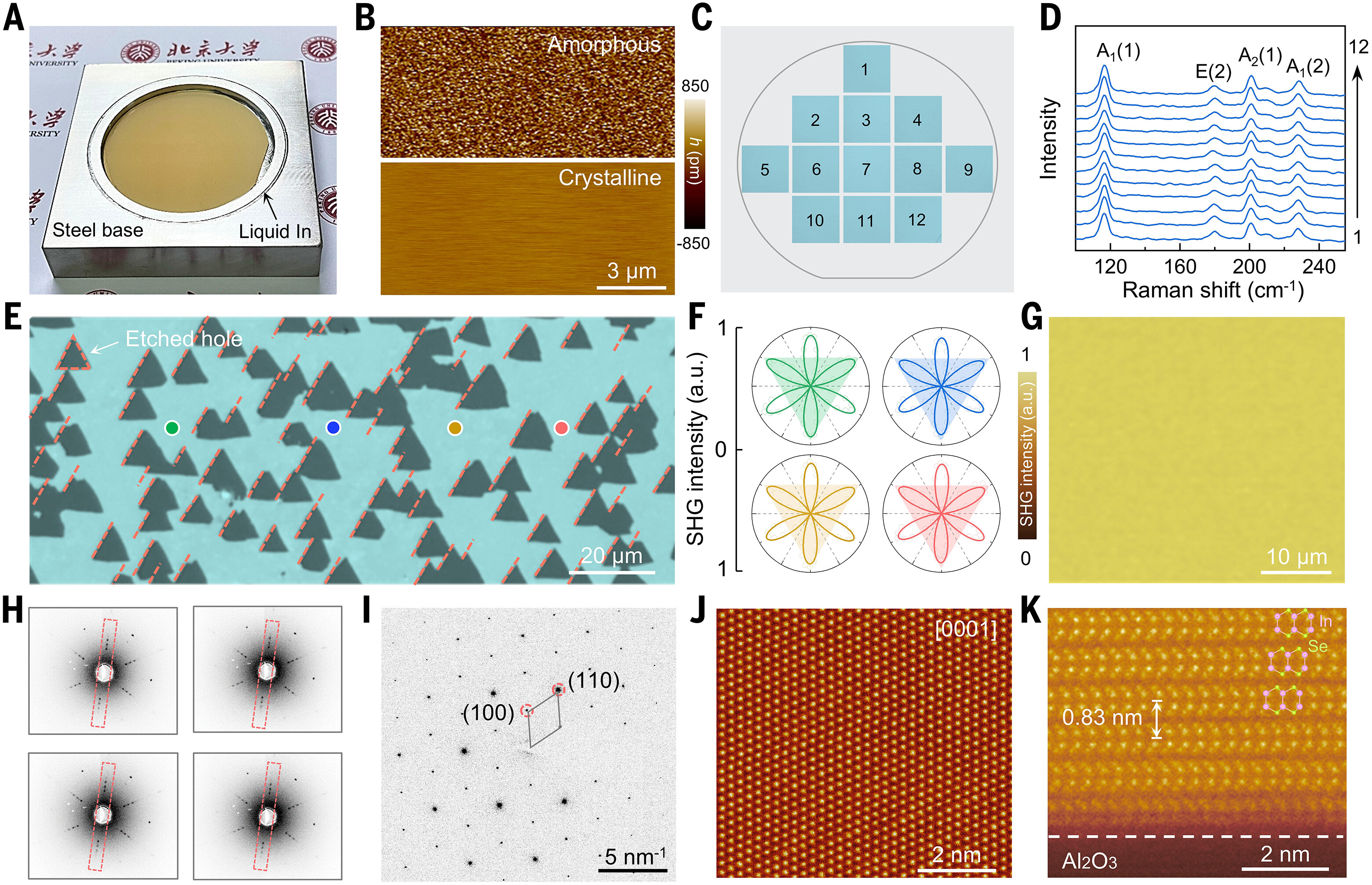

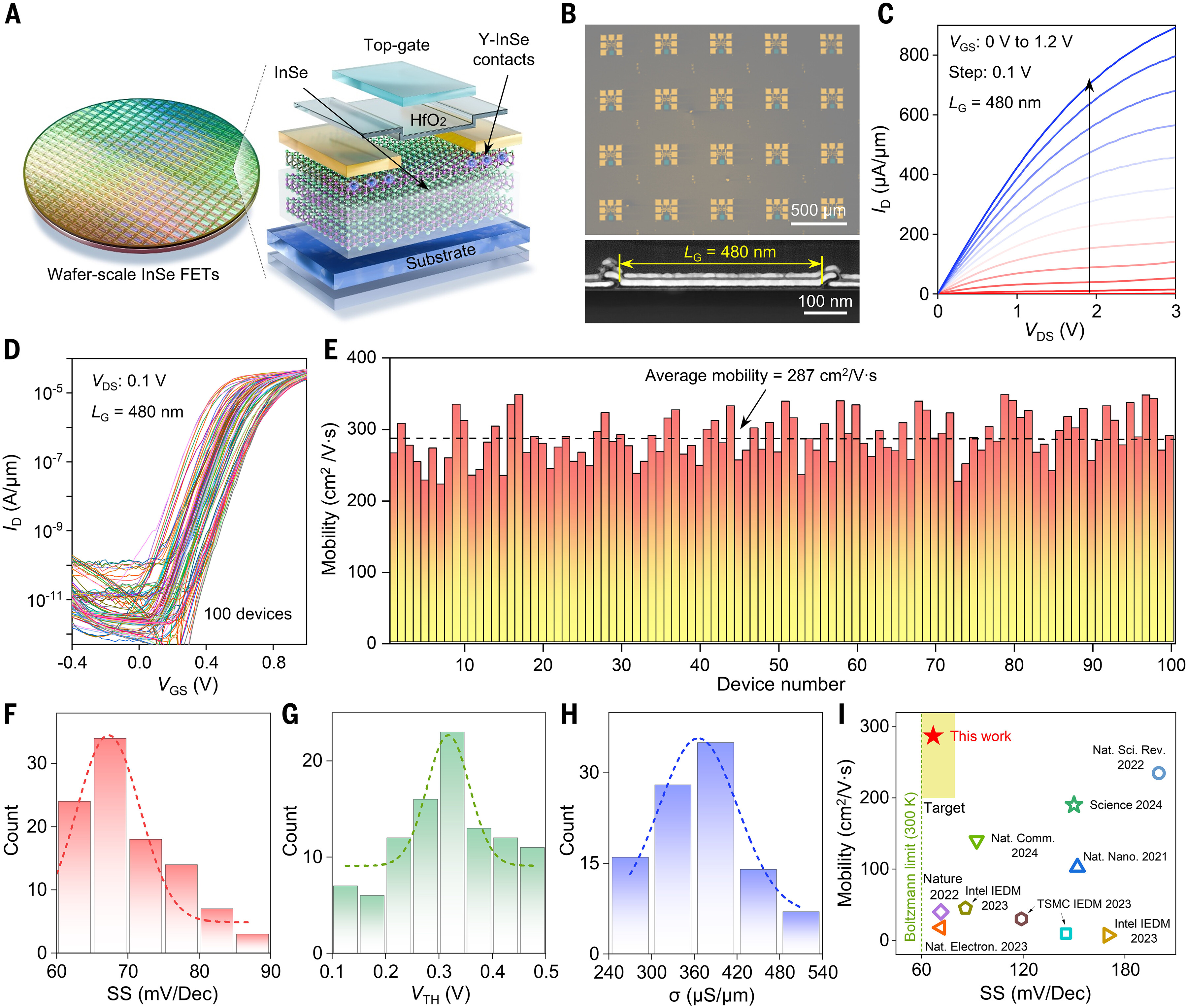

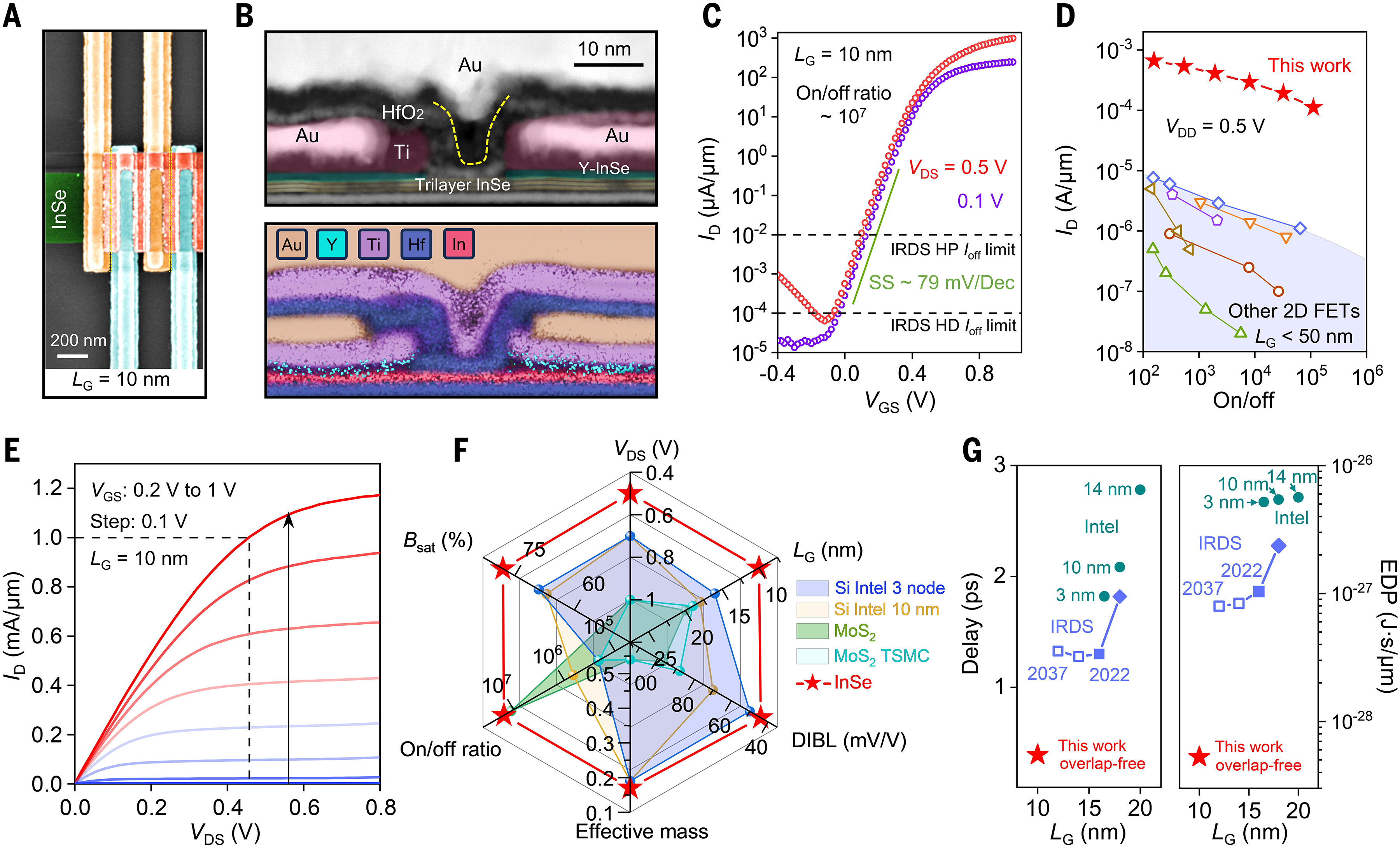

生长方法:通过预沉积非晶 InSe 严格控制化学计量比 1:1, 钢槽和熔融石英之间用 In 液封保持化学计量比。

生长机制:SLS, 非晶 InSe 在富 In 液态界面重结晶到晶体 InSe 一侧,

InSe 为 $C_\text{3v}$ 对称,菱方(ABC)堆积。InSe.cif

费米能级钉扎效应 (Fermi-level pinning effect)

简单来说,费米能级钉扎效应是指半导体的费米能级被“钉”在某个特定的能量位置,不再轻易随掺杂浓度的改变或外加电场的变化而移动的现象。

通常情况下,在半导体中,通过掺杂(比如在硅中掺入磷或硼),我们可以改变材料中电子或空穴的浓度,从而使费米能级在禁带中上升或下降。

然而,在某些情况下,尤其是在半导体的表面或界面,由于存在大量的表面态(surface states)或缺陷态(defect states),费米能级会被“固定”在这些态的能量位置附近。

为什么会发生钉扎?

其核心原因在于高密度的表面/界面态。

- “陷阱”一样的存在:这些表面态就像大量的“陷阱”,可以捕获或释放大量的电子或空穴。

- 缓冲效应:

- 当我们试图通过n型掺杂提高费米能级时,增加的电子会优先填充到这些空的表面态中,而不是进入导带,从而阻止了费米能级的上升。

- 反之,当我们试图通过p型掺杂降低费米能级时,表面态会释放出电子来填充价带的空穴,从而阻止了费米能级的下降。

由于这些表面态的密度非常高,它们就像一个巨大的电荷“缓冲池”,有效地将费米能级“钉”在了它们的能量位置上。

主要影响和意义

费米能级钉扎效应对理解和制造半导体器件至关重要,尤其是在金属-半导体接触中,它直接影响肖特基势垒(Schottky barrier) 的高度。

- 理想情况(无钉扎):根据肖特基-莫特模型(Schottky-Mott model),肖特基势垒的高度应该由金属的功函数和半导体的电子亲和能共同决定。这意味着,通过选择不同功函数的金属,我们可以精确地调控势垒的高度。

- 现实情况(有钉扎):由于费米能级钉扎,无论我们使用哪种金属,半导体界面的费米能级都被钉扎在某个固定位置。这导致肖特基势垒的高度几乎与金属的功函数无关,而是主要由钉扎位置决定。

这个效应解释了为什么在许多实验中,测得的肖特基势垒高度并不像理论预测的那样随金属功函数发生显著变化。

总而言之,费米能级钉扎是由于半导体表面或界面的高密度缺陷态导致费米能级被固定的一种现象,它对金属-半导体接触的电学特性有着决定性的影响。

AI 生成,仅供参考。